# Optimization of an On-chip Active Cooling System Based on Thinfilm Thermoelectric Coolers: Extended Discussion

Jieyi Long<sup>†</sup>, Seda Ogrenci Memik<sup>†</sup>, Matthew Grayson<sup>†</sup>, and Semail Ulgen Yildirim<sup>¶</sup>

<sup>†</sup>Department of EECS, Northwestern University, Evanston, IL 60208 USA jieyi-long@northwestern.edu

Abstract— In this paper, we explore the design and optimization of an on-chip active cooling system based on thinfilm thermoelectric coolers (TEC). We start our investigation by establishing the compact thermal model for the chip package with integrated thin-film TEC devices. We observe that deploying an excessive number of TEC devices and/or providing the TEC devices with an improper supply current might adversely result in the overheating of the chip, rendering the cooling system ineffective. A large amount of supply current could even cause the thermal runaway of the system. Motivated by this observation, we formulate the deployment of the integrated TEC devices and their supply current setting as a system-level design problem. We propose a greedy algorithm to determine the deployment of TEC devices and a convex programming based scheme for setting the supply current levels. Leveraging the theory of inverse-positive matrix, we provide an optimality condition for the current setting algorithm. We have tested our algorithms on various benchmarks. We observe that our algorithms are able to determine the proper deployment and supply current level of the TEC devices which reduces the temperatures of the hot spots by as much as 7.5 °C compared to the cases without integrated TEC devices.

# I. INTRODUCTION

A S THE manufacturing technology steps into the nanometer regime, power density has become a limiting factor for integrated circuit design. Heat dissipated highly unevenly in the active silicon layer, with the peak localized heat fluxes (> 300 W·cm-2) being an order of magnitude larger than the average value across the entire chip [1]. This creates high temperature spots, posing threats on the reliability and performance of the entire chip. Thus, removal of the high-density heat fluxes becomes a crucial task of the chip cooling systems.

Most of the current cooling technologies fall into the category of *passive cooling*, where heat produced by the chip is removed via conduction and convection. In order to improve the efficiency of the heat exchange system, remarkable progress has been made in recent years in the development of heat transport materials and advanced heat exchanger structures such as nanotubes and microchannels [2, 3]. These passive cooling technologies are most effective in removing heat from bulks where heat is distributed evenly. However, they are not as efficient when the chip presents high

<sup>¶</sup>Mathematics Department, Northwestern University, Evanston, IL 60208 USA sulgen@math.northwestern.edu

degrees of spatial power density variation. The inability to provide localized cooling at the hot spots might result in overdesign of the heat exchange system, leading to excessive cooling cost. Cooling cost is already a major item in overall system cost. In data centers, the cooling energy cost has surpassed the energy consumption of the computation equipment [1].

On the other hand, by making use of specially designed miniature heat pumps, *active cooling* technologies can provide site-specific and on-demand cooling, promising new opportunities in cost effective cooling [1, 4-6]. More profoundly, the capability of providing tunable cooling at a fine granularity has significant implications on the thermal aware design of the entire chip. Potentially, the active cooling system, the thermal monitoring system, and the architecture-level thermal management mechanisms [7] can operate synergistically to achieve enhanced performance under a safe operating temperature.

In order to bring this vision into reality, two major hurdles need to be overcome, namely the technology for manufacturing on-chip active coolers and design automation of the cooling system. Recently, intensive research effort has been devoted to multiple candidate active cooling schemes, including integrated thermoelectric cooler (TEC) [1, 6], miniscale vapor compression [8], and miniature capillary pump loop [9]. Among these techniques, integrated TEC is the most accessible one. Off-the-shelf macroscopic TEC devices have long been available [10]. Very recently, Intel researchers have demonstrated the first viable on-chip thin-film TEC manufacturing technology, which has the potential to enable a wide range of currently thermally limited applications [1].

In spite of these promising results in the manufacturing technology, system-level design automation of active cooling system remains largely unexplored. In this paper, we investigate the design and optimization of an on-chip active cooling system based on the recently developed super-lattice thin-film thermoelectric coolers [1]. More specifically, we focus on the following active cooling system configuration problem: Indentifying (1) the deployment of TEC devices, i.e. the regions of the silicon layer that need to be covered by TEC devices; (2) the supply current setting of the on-chip TEC devices. The resulting cooling system should guarantee the operating temperature to remain within the allowable range under the worst-case power profile. We propose an optimization framework for this problem and have tested it

This work was partially supported by AFOSR FA9550-09-1-0237. A Preliminary version of this paper appears in Design, Automation and Test in Europe, 2010.

using various benchmarks. We observe that our algorithm was able to bring down the temperatures of the hot spots by as much as 7.5 °C (compared to the cases without integrated TEC devices). The total power consumption of the resulting cooling system is reasonably small (around 2 W). Moreover, for all benchmarks, the execution time of our algorithm is less than 3 minutes.

In summary, our contribution lies in the following aspects:

- We conduct the first architectural level study of the active cooling system based on integrated TEC devices;

- We reveal the cooling system thermal runaway phenomenon;

- We propose a greedy deployment algorithm and a convex programming based supply current setting algorithm;

- We lay out the theoretical foundation for the analysis of the thermoelectric cooling system by extending the theory of inverse-positive matrix [11].

- We analyze the optimality of the current level configuration algorithm using our proposed thermoelectric cooling system analysis framework.

The remainder of the paper is organized as follows. Section II gives an overview of the related works. In Section III, the design of an on-chip active cooling system based on thin-film thermoelectric coolers is presented, followed by the in-depth discussion of our proposed compact thermal model of the entire chip package in Section IV. We introduce the optimization framework for the cooling system in Section V. Experimental results are presented in Section VI. Finally, we conclude our work with a summary in Section VII.

# II. RELATED WORKS

There has been a few early-stage works concerning the optimization of TEC devices. Abramzon examines the optimal parameters (such as the height/area ratio) for a single TEC device using a numerical optimization approach [12]. Hou *et al.* propose an analytical framework to determine the optimal height of the TEC devices [13]. These works concentrate on the optimization of the physical parameters of the TEC devices. To the best of our knowledge, our work is the first attempt to systematically study the system level optimization problem of the integrated TEC-based active cooling system and evaluate the impact of the active cooling system on the overall thermal behavior of the entire chip package.

# III. ACTIVE COOLING SYSTEMS LEVERAGING THIN-FILM THERMOELECTRIC COOLERS

#### A. Basics of Thin-Film Thermoelectric Cooler

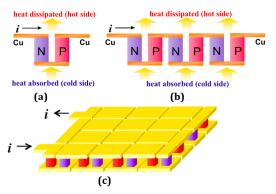

A TEC device is typically composed of a couple of dissimilar semiconductor strips connected electrically in series and thermally in parallel (Figure 1(a)). The principle behind the thermoelectric cooler is the Peltier effect: when an electrical current is sent through the strips, heat is absorbed at one side and released at the other side. Denoting the heat flux absorbed from the cold side as  $q_c$  and dissipated from the hot side as  $q_h$  at temperatures  $\theta_c$  and  $\theta_h$ , respectively, the following equations describe the principle of thermoelectric cooling

Figure 1. (a) The side view of a single TEC device (b) multiple TEC devices connected electrically in series and thermally in parallel (c) the 3D view of a 4x4 array of thin-film TEC devices.

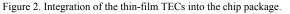

Figure 3. Compact thermal model of the chip package.

[13]:

$$q_c = \alpha i \theta_c - \frac{1}{2} r i^2 - k \left( \theta_h - \theta_c \right)$$

(1)

$$q_h = \alpha i \theta_h + \frac{1}{2} r i^2 - k \left( \theta_h - \theta_c \right)$$

<sup>(2)</sup>

where *i* is the electrical supply current of the TEC device;  $\alpha$  is the Seebeck coefficient of the TEC device; *r* and  $\kappa$  are the electrical resistance and thermal conductance of the device, respectively. The first term in these two equations describes the Peltier cooling effect. The second term is due to Joule heating that occurs in the TEC device – half of the Joule heat is dissipated at the cold side and the other half at the hot side. The third term is contributed by heat conductance from the hot side to the cold side.

According to Equations (1) and (2), the input power of a TEC device is equal to

$$p_{TEC} = q_h - q_c = ri^2 + \alpha i \cdot \Delta \theta \tag{3}$$

In steady state, the input power of the TEC devices will be converted to heat in the chip package before being dissipated to the ambient. Hence, an excessive deployment of TEC devices and/or improper setting of the TEC supply current levels could lead to the overheating of the chip package.

It is worth to note that although the above equations are widely used in the literature, they have omitted the Thompson effect, which accompanies with the Peltier effect [14]. The Thompson effect is caused by the dependence of the Seebeck coefficient on temperature. However, the Thompson effect can be accounted for by substituting  $\alpha$  with  $(\alpha_H + \alpha_C)/2$ , where  $\alpha_H$

and  $\alpha_C$  are the Seebeck coefficients at the highest and lowest allowable operating temperature of the system, respectively [14]. In our model, we have adopted this more accurate approximation.

In order to enhance the cooling effect, multiple TEC devices can be connected electrically in series and thermally in parallel (Figure 1(b)). Figure 1(c) shows the 3D view of a 4 x 4 array of super-lattice thin-film TEC devices [1]. Thin-film TEC devices occupy small areas. For instance, a 7 x 7 array of thin-film TEC devices has a lateral dimension of about 3.5 mm x 3.5 mm [1]. Hence, the lateral area of a single TEC device can be estimated by 0.5 mm x 0.5 mm.

## B. Thin-film Thermoelectrics based Active Cooling System

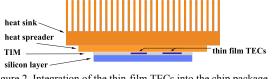

Figure 2 illustrates the integration of the thin-film TEC devices into the chip package [1]. The thin-film TEC devices are immersed in the thermal interface materials (TIM) layer, lying between the silicon layer and the heat spreader layer.

The supply current of the on-chip TEC devices is provided by an external source via one or multiple pins. In this paper, we focus the simplest setting where only one extra pin is added to the chip package. As a result, we assume that the supply current of all the on-chip TEC devices are the same. Allowing only one extra pin is desirable to the high performance microprocessor systems for which the thin-film TEC technology is intended. These chips are already restricted in pin usage (a maximum number of pins would be desirably allocated for I/O etc.) and have limited room for extra pins.

The deployment and the supply current levels of the TEC devices need to be carefully determined to prevent the chip package from overheating. We will provide the formal definition of the cooling system optimization problem in Section V. Before that, we first present our compact thermal model for chip packages with integrated TEC devices in Section IV.

# IV. COMPACT THERMAL MODEL FOR CHIP PACKAGE WITH ON-CHIP THERMOELECTRIC COOLERS

As a design requirement, the cooling system should guarantee that the peak *steady state* temperature of the silicon layer stays below the maximum allowable temperature under the worst-case power profile. The compact thermal model derived in this section is intended for the steady state analysis of the chip package.

#### A. Compact Thermal Model for the Chip Package

There is a well-known duality between heat transfer and electrical phenomena. The heat flow can be treated as "current" passing through thermal conductance, creating temperature differences analogous to "voltage" drops. Such equivalency has been leveraged to develop *compact thermal models* for chip packages [7]. Figure 2 demonstrates the typical chip package for high-performance microprocessors. The silicon layer is placed against a heat spreader layer, made of aluminum or copper, with a TIM layer in between. The heat spreader layer is in turn placed against a heat sink cooled by a fan [7].

In order to derive a compact thermal model for the chip package, each layer is first dissected into smaller tiles. Next, a thermal conductance network can be constructed, where each node corresponds to a tile and each edge represents the thermal conductance between adjacent tiles. Air convection is described by a thermal conductor between the nodes in the heat sink layer and the ambient node. The ambient temperature can be modeled by a constant voltage between the ambient node and the hypothetical ground node representing the absolute zero temperature. Power dissipation in the silicon layer is modeled as current sources. The left part of Figure 3 demonstrates the dissection of the layers into tiles, while the right part depicts the conductance network for the shaded portion of the package. Notice that the thermal capacitance is not included in our model since we are focusing on the steady state behavior of the package.

Validation of existing architecture-level thermal simulation tools based on this model has shown that the compact model achieves excellent agreement with the accurate finite element models [7, 15].

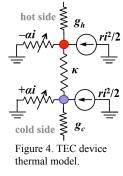

# B. Compact Thermal Model for Systems with TECs

We propose a thermal model for the TEC device based on Equation (1) and (2) as depicted in Figure 4. The two nodes represent the hot side and the cold side of the device. A thermal conductor  $\kappa$  connecting the two nodes models the term  $\kappa(\theta_h - \theta_c)$  in Equation (1) and (2). The Joule heating effect can be described by two heat sources connected to the hot side and cold side node, each having the magnitude

of  $ri^2/2$ . The Peltier heat  $\alpha i \theta_c$  absorbed at the cold side can be described by a thermal conductor  $\alpha i$  connecting the cold side and the ground node which represents the absolute zero temperature. Likewise, the Peltier heat  $\alpha i\theta_h$  released at the hot side can be modeled by a negative thermal conductor  $-\alpha i$ connecting the hot side and the ground. We note that the values of these two conductors depends on the supply current. Hence, in Figure 4, arrows were used to indicate that they are "tunable conductors". In addition, we place two thermal conductors  $g_h$  and  $g_c$  at the hot/cold nodes to account for the contact thermal resistance between the hot/cold side and the rest of the package. Such thermal conductors which lie between the hot side and the ambient end up playing an important role in the thermal runaway problem. We remind the reader that Figure 4 represents a thermal flow circuit and the physical current *i* does not flow through any of these "conductances".

As mentioned above, the TEC devices reside in the TIM layer. After the set of silicon tiles that need to be covered by TEC devices is determined, we simply substitute the corresponding TIM node with the thermal model of the TEC device. We note that after the substitution, at a fixed value of TEC supply current, *the compact thermal model for the package is still a linear network*. Hence, standard linear

network analysis techniques can be applied to study the thermal behavior of the package.

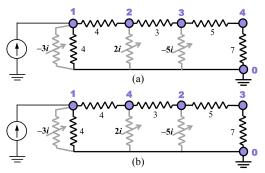

# C. Thermal Steady State Analysis

The thermal steady state of the network can be computed using the nodal analysis technique [16]. Let us use notations *SIL*, *HOT*, and *CLD* to denote the set of nodes in the silicon layer, the hot side, and the cold side of the TEC devices, respectively. We use a vector **p** to represent the input heat power at each node, where  $p_k$  equals the heating power of the transistors inside the silicon tile if  $k \in SIL$ ,  $ri^2/2$  if  $k \in HOT \cup$ *CLD*, and 0 otherwise. Then, the steady state temperature profile **θ** is related to the power profile **p** by a system of linear equations

$$(\mathbf{G} - i\mathbf{D})\mathbf{\theta} = \mathbf{p} \tag{4}$$

where matrices G and D are defined in the following

$$\mathbf{G} = \begin{pmatrix} \sum_{0 \le l \le n} g_{1l} & -g_{12} & \cdots & -g_{1n} \\ \vdots & \vdots & \vdots & \vdots \\ -g_{k1} & \cdots & \sum_{0 \le l \le n} g_{kl} & \cdots & -g_{kn} \\ \vdots & \vdots & \vdots \\ -g_{n1} & -g_{n2} & \cdots & \sum_{0 \le l \le n} g_{nl} \end{pmatrix} \mathbf{D} = \begin{pmatrix} \alpha_1 & 0 & \cdots & 0 \\ \alpha_2 & \cdots & 0 \\ & \alpha_k & \vdots \\ 0 & \cdots & \cdots & 0 \\ 0 & \cdots & 0 & \alpha_n \end{pmatrix}$$

(5)

Here  $g_{kl}$  is the thermal conductance between node k and node l  $(g_{kl}$  is zero if node k and node l are not adjacent in the network);  $\alpha_k$  equals to  $+\alpha$  if  $k \in HOT$ ,  $-\alpha$  if  $k \in CLD$ , and 0 otherwise, and  $\alpha$  accounts for the transfer of Peltier heat in the network.

Matrix **G** has several special structural properties essential to our proposed active cooling system optimization algorithm. They are captured by the following definitions and Theorem 1. For the sake of brevity, theorem 1 and several theorems in Section V are stated without proofs. The formal proofs are provided in Appendix A.

*Definition 1:* We call a network an *irreducible network* if and only it contains at least one path between any given pair of nodes.

Given an  $n \ge n$  symmetric matrix  $\mathbf{M} = (m_{ij})_{n \ge n}$ , we can construct a corresponding network containing n nodes. We connect the  $i^{\text{th}}$  and  $j^{\text{th}}$  node by an undirected edge if  $m_{ij} \ne 0$ .

*Definition 2:* A matrix is called an *irreducible matrix* if and only if its corresponding network is an irreducible network.

Definition 3: An  $n \ge n$  real matrix **M** is positive definite if  $\mathbf{x}^{T}\mathbf{M}\mathbf{x} > 0$  for all non-zero vectors  $\mathbf{x}$  with real elements.

*Definition 4:* A *Stieltjes matrix* is a real symmetric matrix with non-positive off-diagonal elements [11].

*Theorem 1:* The matrix **G** defined in Expression (5) is an irreducible positive definite Stieljes matrix.

# V. OPTIMIZATION OF THE ACTIVE COOLING SYSTEM

## A. Problem Definition

Based on the discussions in Sections III and IV, we define

active cooling system configuration problems as follows.

*Problem 1* (Cooling System Configuration): Given: 1)  $p \times q$  tiles representing the silicon layer where each tile has the same area as a TEC device, and 2) the worst case power consumption of each tile;

Determine: 1) the minimal set of tiles that needs to be covered by the TEC devices, and 2) the proper supply current of the TEC devices;

Objective: the peak steady state temperature of the silicon layer does not exceed the maximal allowable temperature.

#### B. Optimization Algorithms

Figure 5 provides the pseudo code of our algorithm, which solves the deployment problem following the greedy strategy. It works in an iterative manner. In the beginning, it identifies the set of tiles T whose temperature exceeds the maximum allowable operating temperature  $\theta_{max}$  and covers these tiles with TEC devices (Line 4, 7). Then, a subroutine will be invoked to compute the supply current of the TEC devices that minimizes the peak temperature of the tiles in the silicon layer for the given TEC deployment (Line 8). We will elaborate on this subroutine in the subsequent section. Adding more TEC devices into the package has two consequences: The temperatures of the tiles that are covered by these TEC devices may decrease; however, the temperatures of other tiles might increase since the new set of TEC devices dissipate an extra amount of heat in the package. Hence, in each iteration, after adding TEC devices, we update set T (Line 10). If T is an empty set, the peak tile temperature must be below  $\theta_{max}$ . The algorithm then returns true, indicating a proper deployment is found (Line 11~12). If all the tiles whose temperature are above  $\theta_{max}$  have already been covered by the TEC devices, the algorithm returns false, indicating that it failed to find a proper TEC deployment (Line 13~14). Otherwise, the main loop proceeds to its next iteration.

## 1) The peak tile temperature minimization problem

This section would elaborate on the subroutine for peak tile temperature minimization (invoked in the 8<sup>th</sup> line of Figure 5).

*Problem 2* (Peak tile temperature minimization): Given the deployment of the TEC devices, determine the supply current

| ALGORITHM GreedyDeploy( <b>p</b> )<br>INPUT: <b>p</b> // the worst case power consumption of each tile<br>OUTPUT: $S_{TEC}$ // the set of tiles that need TEC devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 Begin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1 DEGIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2 $S_{TEC} = \Phi;$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3 Solve $\mathbf{G}\mathbf{\dot{\theta}} = \mathbf{p}$ ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2 $S_{TEC} = \Phi$ ;<br>3 Solve $G\theta = p$ ;<br>4 $T = \{tile_k \mid tile_k.temperature > \theta_{max}\};$<br>5 WHILE (True) BEGIN<br>7 $S_{TEC} = S_{TEC} \cup T;$<br>8 Find $i_{opt}$ , which minimizes the peak tile temperature;<br>9 Solve $(G - i_{opt}D)\theta = p;$<br>10 $T = \{(i = i_{opt}), (i = $ |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6 While (True) Begin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7 $S_{TEC} = S_{TEC} \cup T;$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8 Find $i_{ont}$ , which minimizes the peak tile temperature;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9 Solve $(\mathbf{G} - i_{opt}\mathbf{D})\mathbf{\theta} = \mathbf{p};$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10 $T = \{tile_k \mid tile_k.temperature > \theta_{max}\};$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11 IF $(T = \Phi)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 12 <b>Return</b> True;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 13 IF $(T \subset S_{TEC})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 14 <b>RETURN False</b> ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15 END                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 16 End                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Figure 5. The greedy algorithm for the deployment problem.

of the TEC devices which minimizes the maximum temperature of the tiles.

This problem can be formulated as follows:

minimize

$$\max\{\theta_k(i) \mid \forall k \in SIL\}$$

(6)

subject to  $(\mathbf{G} - i\mathbf{D})\mathbf{\theta} = \mathbf{p}, i \ge 0$  (7)

In the following, we will develop a convex programming based algorithm for this problem. Firstly, we show that there exists an upper limit  $\lambda$  for the supply current of the TEC devices. Any supply current level larger than  $\lambda$  would cause thermal runaway. Mathematically, as the supply current approaches  $\lambda$ , the temperature of each tile approaches infinity. We provide a polynomial time algorithm to calculate  $\lambda$ . Then, we propose a conjecture in matrix theory. Based on the conjecture, we provide a sufficient condition for the cost function (6) to be a convex function of the supply current *i* over  $[0, \lambda)$ .

2) The active cooling system thermal runaway phenomenon

We will leverage the theory of inverse-positive matrix [11] to show the existence of the upper limit  $\lambda$  in this section.

Theorem 2: Given a positive definite irreducible Stieltjes matrix G and a real diagonal matrix D with at least one positive element, define

$$\lambda = \inf \left\{ \frac{\boldsymbol{\theta}^{\mathrm{T}} \mathbf{G} \boldsymbol{\theta}}{\boldsymbol{\theta}^{\mathrm{T}} \mathbf{D} \boldsymbol{\theta}} \middle| \boldsymbol{\theta}^{\mathrm{T}} \mathbf{D} \boldsymbol{\theta} > 0 \right\}$$

Let  $\mathbf{A} = \mathbf{G} - i\mathbf{D}$ . We have the following:

1) For any  $i \in [0, \lambda)$ , **A** is positive definite.

2) When  $i = \lambda$ , **A** is singular and semidefinite.

3) For any  $i \in [\lambda, +\infty)$ , **A** is not positive definite.

*Theorem 3:* Given matrix **A** and real number  $\lambda$  as defined in Theorem 2 and denoting  $\mathbf{H} = \mathbf{A}^{-1}$ , for any  $1 \le k, l \le n$ , we have

$$\lim_{i \to \lambda^{-}} h_{kl}(i) = +\infty \tag{8}$$

where symbol  $h_{kl}(i)$  represents the element of **H** in the  $k^{\text{th}}$  row and the  $l^{\text{th}}$  column (as a function of *i*).

Figure 6 depicts  $h_{kl}(i)$  as a function of *i*. Note that according to Equation (4),  $\boldsymbol{\theta} = \mathbf{A}^{-1} \cdot \mathbf{p} = \mathbf{H} \cdot \mathbf{p}$ . Thus, the physical interpretation of  $h_{kl}$  is the temperature of node *k* if a unit of power is input at node *l*. Theorem 2 reveals that if there is one node in the network that has non-zero input power, then, as *i* approaches  $\lambda$ , the temperature of each node approaches infinity, indicating thermal runaway.

Figure 6.  $h_{kl}(i)$  as functions of the supply current *i*.

The physical interpretation of the thermal runaway is as follows.  $\lambda$  represents the input current level which causes the active cooling system to have zero heat pumping capability since Peltier cooling is offset by ohmic heating and heat conduction. In the thermoelectric literature, this occurs when the coefficient of performance of the thermoelectric cooler becomes zero [17]. Similar situations have been investigated but under different boundary conditions [17]. The above

discussion reveals we should restrict the search of the current level that minimizes the maximum silicon layer temperature within  $[0, \lambda)$ .

This upper limit  $\lambda$  can be calculated using a binary search based on Theorem 1. Cholesky decomposition ( $O(n^3)$  time complexity) is employed to check whether a matrix is positive definite [18].

3) The convexity of the cost function

In this section, based on a conjecture, we provide a sufficient condition for the maximum temperature of the tiles to be a convex function of *i* over  $[0, \lambda)$ .

*Definition 5:* Given a vector **r**, denote the  $k^{\text{th}}$  element of **r** by  $r_k$ . We define notation DIAG(**r**) to be a square diagonal matrix with all off-diagonal elements being zero and the diagonal element in the  $k^{\text{th}}$  row and  $k^{\text{th}}$  column equals to  $r_k$ .

*Conjecture 1:* Given an  $n \ge n$  positive definite Stieltjes matrix **S**, denote  $\mathbf{R} = \mathbf{S}^{-1}$ . Denoting the  $k^{\text{th}}$  and  $l^{\text{th}}$  row vector of **R** by  $\mathbf{r}_k$  and  $\mathbf{r}_l$ , then DIAG( $\mathbf{r}_k$ )·**R**·DIAG( $\mathbf{r}_l$ ) is positive definite for any  $1 \le k, l \le n$ .

Although we have not yet been able to prove this conjecture theoretically, we have randomly generated millions of positive definite Stieltjes matrices and verified this property in all cases. Hence, it seems that this property is applicable in all practical cases.

*Theorem 4:* Given matrix **H** and real number  $\lambda$  as defined in Theorem 2, if Conjecture 1 holds true, then every element  $h_{kl}(i)$  of matrix **H** is a convex function of supply current *i* over  $[0, \lambda)$ .

Theorem 3 and Theorem 4 characterize  $h_{kl}(i)$  over range [0,  $\lambda$ ): it is a nonnegative convex function which approaches  $+\infty$  when *i* approaches  $\lambda$ . Figure 6 illustrates these properties.

According to Equation (4),  $\mathbf{\theta} = \mathbf{A}^{-1} \cdot \mathbf{p} = \mathbf{H} \cdot \mathbf{p}$ . Hence, the temperature of the  $k^{\text{th}}$  node in the network equals

$$\theta_{k}(i) = \frac{1}{2}ri^{2}\sum_{l \in HOT \cup CLD} h_{kl}(i) + \sum_{l \in SIL} \left(h_{kl}(i) \cdot p_{l}\right) = \frac{1}{2}ri^{2} \cdot \eta(i) + \zeta(i) \quad (10)$$

We note that if Conjecture 1 is true, functions  $\eta(i)$  and  $\zeta(i)$  are both convex functions of *i* since they are positive weighted sums of convex functions. However, the product term  $ri^2\eta(i)/2$  is not guaranteed to be a convex function in general. In the following, we derive a simple sufficient condition to check whether  $\theta_k(i)$  is a convex function. The verification of the sufficient condition can be performed in polynomial time. According to Equation (10), we have

$$\theta_{k}''(i) = r\eta(i) + ri\eta'(i) + \frac{1}{2}ri^{2}\eta''(i) + \zeta''(i)$$

(11)

$\geq r\eta(i) + r\eta'(i) \cdot i$

Noticing that  $\eta'(i)$  is an increasing function since  $\eta(i)$  is convex, we have the following sufficient condition:

*Theorem 5:* Assuming Conjecture 1 holds, if the following problem (12) is infeasible, then  $\theta_k(i)$  is convex over  $[i_t, i_{t+1}]$ . Here,  $i_t$  and  $i_{t+1}$  are real values satisfying  $0 \le i_t < i_{t+1} < \lambda$ .

$$\eta(i) + r\eta'(i_{t}) \cdot i < 0, \ i \in [i_{t}, \ i_{t+1}]$$

(12)

In the above formulation,  $\eta'(i_t)$  is a constant that equals to the derivative of  $\eta(i)$  at  $i_t$ . The left hand side of the inequality is a convex function, since it is the sum of a convex function and a linear function. Hence, problem (12) is a convex feasibility problem, which can be solved in polynomial time. In order to calculate  $\eta'(i_t)$ , we note that d**H** / d*i* = **HDH**. Since

$$\eta'(i) = \sum_{l \in HOT \cup CLD} h_{kl}'(i)$$

(13)

$\eta'(i_t)$  can be determined accordingly in polynomial time.

We note that  $\theta_k(i)$  is twice differentiable over  $[0, \lambda)$ . Hence, the convexity of the function over each of the sub-ranges implies the convexity of the function over  $[0, \lambda)$ . We thus reach the following theorem which enables us to check whether  $\theta_k(i)$  is convex over  $[0, \lambda)$  in polynomial time.

*Theorem 6:* Assuming Conjecture 1 holds, given any finite sequence of real numbers satisfying  $0 = i_0 < ... < i_t < i_{t+1} < ... < i_m = \lambda$ , if convex feasibility problem (12) is infeasible for each  $[i_t, i_{t+1}]$ , then  $\theta_k(i)$  is convex over  $[0, \lambda)$ .

In theorem 6, the increasing sequence  $\{i_i\}$  can be chosen arbitrarily. For instance, we can chose  $0 = i_0 < i_1 = \lambda$ . This would minimize the runtime of the checking process. However, the optimality check would be quite pessimistic since  $\eta'(0)$  is a very loose lower bound for  $\eta'(i)$  over  $[0, \lambda)$ . Dividing  $[0, \lambda)$  into more sub-ranges would increase the accuracy of the lower bound for  $\eta'(i)$  at the expense of runtime.

#### *4)* Algorithm minimizing the peak tile temperature

Based on the above discussions, we developed a convex programming based algorithm for Problem 2. In the beginning, we determine the upper limit  $\lambda$ . Then, we employ the gradient descent method to solve formulation (6~7) [18]. At the end, we perform an additional optimality check based on Theorem 4. If Conjecture 1 is true and the problem instance passes the optimality check, then, formlation (6~7) is a convex optimization problem. Thus, the solution obtained by the gradient descent method is guaranteed to be optimal.

#### VI. EXPERIMENTAL RESULTS

We have implemented our optimization framework in C++ and evaluated our proposed algorithms on various benchmarks. All the experiments were carried out on a Linux server with four 2.8 GHz Intel<sup>®</sup> Xeon<sup>™</sup> processors and 1 GB memory. In our implementation, the physical parameters (Seebeck coefficient, electrical resistivity and thermal conductivity) of the thin-film TEC device provided by Chowdhury et al. [1] are used. Other parameters such as the silicon thermal conductivity, convection, etc., were set according to an existing thermal simulator, HotSpot 4.1 [7]. We have first validated our thermal model against HotSpot 4.1 by performing steady state analysis without the TEC devices. For a given floorplan and a set of power traces, we performed steady state analysis using both our model and Hotspot 4.1 and compared the temperature of each tile generated by them. The two results agreed closely - the worst-case difference is less than 1.5 °C. Next, we conducted experiments with our model including the TEC devices to evaluate the impact of the active cooling system on the thermal behavior of the chip package.

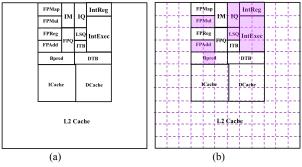

Figure 7. (a) The floorplan of an Alpha-21364-like microprocessor (b) dividing the floorplan into 12x12 tiles.

## A. Experimental Study for a DEC Alpha-21364-Like Chip

Our first set of experiments was performed on a microprocessor floorplan similar to that of a 65nm DEC Alpha-21364 microprocessor (Figure 7(a)) [7]. The silicon die has a dimension of 6 mm x 6 mm. As mentioned in Section III.A, we estimated the lateral area of a single TEC device by 0.5 mm x 0.5 mm. Hence, the silicon die was divided into 12x12 tiles in our experiment (Figure 7(b)). To obtain the worst case power consumption of each silicon tile, we simulated the SPEC2000 benchmark suite [19] using M5 simulator [20] with an embedded architecture level power simulator Wattch [21]. We collected the worst case power consumption of each functional unit and added a 20% margin to them. Based on these numbers, we calculated the worst case power consumption of each tile. As mentioned earlier, the power dissipation of the functional units is highly uneven. The power density of the heavily used units such as integer register (IntReg) can be as high as 282.4 W·cm<sup>-2</sup> while that of L2 Cache is only 25.0 W·cm<sup>-2</sup>. The total worst case power consumption of the chip is 20.6 W. The heavily used units such as integer register, integer execution unit (IntExec), instruction queue (IQ), load and store queue (LSQ), floating point multiplier (FPMul), and floating point adder (FPAdd) consumes 28.1% of the total power while occupying only 10.4% of the total area.

The first row of Table I summarizes our experimental results on the Alpha-21364 microprocessor floorplan. We first computed the steady state of the Alpha-21364 chip without the TEC devices. The temperature of the hottest tile in the silicon layer is given in Column  $\theta_{peak}$  (91.8 °C). Next, we employed our GreedyDeploy algorithm to determine the set of tiles that

TABLE I. EXPERIMENTAL RESULTS FOR THE BENCHMARKS

|       | No TEC             | Greedy Deployment |                    |                       |                              | Full Cover                |                 |

|-------|--------------------|-------------------|--------------------|-----------------------|------------------------------|---------------------------|-----------------|

|       | $\theta_{peak}$ °C | #TECs             | $	heta_{limit}$ °C | I <sub>opt</sub><br>A | <b>Р</b> <sub>TEC</sub><br>W | minθ <sub>peak</sub><br>℃ | SwingLoss<br>°C |

| Alpha | 91.8               | 16                | 85                 | 6.10                  | 1.31                         | 90.2                      | 5.2             |

| HC01  | 90.1               | 12                | 85                 | 6.82                  | 1.26                         | 88.5                      | 3.5             |

| HC02  | 92.5               | 15                | 85                 | 6.90                  | 1.63                         | 90.9                      | 5.9             |

| HC03  | 89.8               | 16                | 85                 | 7.24                  | 1.93                         | 88.3                      | 3.3             |

| HC04  | 90.5               | 16                | 85                 | 6.57                  | 1.57                         | 88.9                      | 3.9             |

| HC05  | 89.9               | 18                | 85                 | 7.10                  | 2.09                         | 88.4                      | 3.4             |

| HC06  | 94.2               | 17                | 89                 | 5.27                  | 1.03                         | 92.6                      | 3.6             |

| HC07  | 91.2               | 14                | 85                 | 8.26                  | 2.24                         | 89.6                      | 4.6             |

| HC08  | 89.4               | 11                | 85                 | 5.05                  | 0.60                         | 87.9                      | 2.9             |

| HC09  | 95.3               | 12                | 88                 | 10.42                 | 3.02                         | 93.8                      | 5.8             |

| HC10  | 90.6               | 14                | 85                 | 7.82                  | 1.97                         | 89.1                      | 4.1             |

| Avg.  |                    |                   |                    |                       | 1.70                         |                           | 4.2             |

need to be covered by TEC devices. The maximum allowable tile temperature was set to 85 °C (Column  $\theta_{limit}$ ). The GreedyDeploy algorithm determined 16 tiles that need to be covered by TEC devices (Column #TECs). These tiles are shaded in Figure 7(b). It can be seen that only the functional units with high power density (such as IntReg and IntExec) are needed to be covered. Table I also reports the supply current (Column  $I_{opt}$ ) determined by the GreedyDeploy algorithm, as well as the power consumption of the TEC devices (Column  $P_{TEC}$ ). The external power consumed by the TEC devices is reasonably small (1.31 W). Our algorithm is efficient in terms of execution time – the deployment and level configuration algorithms combined terminated within 2 minutes.

We compared our optimization framework with a baseline strategy where every tile is covered by a TEC device with the supply current determined by our convex-programming based peak tile temperature minimization algorithm (Section V.C). The experimental results are listed in the two columns under the Full Cover label. It is noticeable that at the optimal supply current, the peak tile temperature is as high as 90.2 °C (Column min $\theta_{peak}$ ), 5.2 °C higher (Column SwingLoss) than what could be achieved by our GreedyDeploy algorithm. As mentioned in Section III.B, the external power consumed by the TEC devices would counteract their cooling effect. This phenomenon reveals that placing excessive TEC devices would decrease the efficiency of the active cooling system.

#### B. Experimental Study for Hypothetical Chips

The second set of experiments was conducted on 10 hypothetical chips, each represented by a 12x12 array of tiles corresponding to a 6 mm x 6 mm floorplan. For each chip, we first randomly divided the floorplan into several functional units, each containing between 5 and 15 tiles. In order to imitate the non-uniform power distribution, we randomly selected two units and assigned them higher power density than the rest. Typically, the two selected units consume 30% of chip power while occupying 10% of the chip area. The total power consumption of the chip ranges from 15 W to 25 W.

We conducted experiments and a comparison similar to those described in Section VI.A. Rows 2 until 11 of Table I provide the experimental results. We observe that for all the benchmark chips except for HC06 and HC09, the GreedyDeploy algorithm was able to guarantee that the maximum tile temperatures stay below the given limit (85 °C) with reasonably small power overhead (around 2 W). Without the TEC devices, the maximum tile temperature can be as high as 92.5 °C (HC02). Hence, the active cooling swing can reach 7.5 °C. Here the term "cooling swing" refers to the drop of the maximum tile temperature after employing the active cooling system. This conforms to the maximum on-demand cooling swing (5.4 °C to 9.6 °C) reported by Chowdhury *et al.* [1]. Besides, for each benchmark, the execution time of our algorithms is less than 3 minutes.

For benchmark chips HC06 and HC09, our algorithms fail when the maximum allowable temperature is set to 85 °C. This is mainly because the temperatures of the hot spots in these two chips are too high (Column 1). It is beyond the capability of the TEC devices to cool them down to 85 °C. However, when the maximum allowable temperature is set to higher values (89 °C for HC06 and 88 °C for HC09, Column 3), our algorithm would be able to determine proper deployments and supply currents for these two benchmarks.

Finally, similar to the Alpha 21364 case, for these ten benchmark chips, assigning a TEC device to every tile increases the lowest achievable peak tile temperature. Compared to the deployment determined by the GreedyDeploy algorithm, the cooling swing loss is 4.2 °C on average. This confirms our conclusion that allocating excessive TEC devices would reduce the overall efficiency of the active cooling system and the system design process benefits from a systematic approach to this problem.

#### VII. CONCLUSIONS